Základní informace o pamětech NAND Flash

V tomto příspěvku stručně představím paměti NAND Flash, technologii, která od svého vzniku v 80. letech 20. století dominuje na trhu polovodičových pamětí.

Úvod do paměti NAND Flash

Dvě hlavní architektury pamětí Flash jsou paměti NAND a paměti NOR. Tyto názvy odkazují na skutečnost, že jejich paměťová pole jsou uspořádána do jisté míry jako logická hradla NAND a NOR CMOS. První moderní paměť flash představil Masuoka a jeho spolupracovníci ze společnosti Toshiba na mezinárodním setkání IEEE International Electron Devices Meeting v roce 1984. Původně se o paměťových čipech Flash uvažovalo jako o potenciální náhradě čipů EPROM ("Erasable Programmable Read Only Memory"), které v té době dominovaly trhu. Většina tehdy dostupných pamětí EPROM vyžadovala k vymazání dat vystavení ultrafialovému světlu, naproti tomu paměti flash bylo možné vymazat elektricky. Samotný název "Flash" byl zvolen proto, že u těchto pamětí bylo možné vymazat jejich obsah mnohem rychleji než u jiných tehdy dostupných technologií. Hromadná výroba pamětí NAND flash začala v roce 1992, kdy byl představen 16megabitový čip vyrobený 0,7mm technologií v konvenčním izolačním procesu LOCOS.

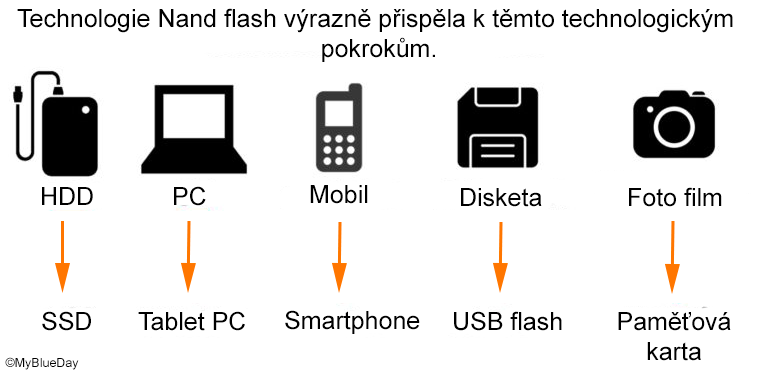

Aplikace pamětí flash se rychle rozšiřovaly díky různým výhodám této technologie: nevolatilitě, rychlému přístupu a robustnosti. Aplikace pamětí Flash lze rozdělit do dvou hlavních mezer. První je pro aplikace ukládání kódu, jako je BIOS osobních počítačů a mobilních telefonů; pro tyto aplikace jsou vhodnější buňky typu NOR vzhledem k jejich vyšší rychlosti náhodného přístupu. Druhou oblastí jsou aplikace pro ukládání souborů, jako jsou digitální fotoaparáty, chytré telefony a tablety; pro tento segment trhu se staly paměťovou technologií buňky typu NAND. Některé z nejpřevratnějších inovací spotřební elektroniky v předchozích 20 až 30 letech by totiž bylo mnohem obtížnější, ne-li nemožné, dosáhnout bez rozsáhlého využití paměťové technologie NAND Flash. To se týká přechodu od disket k USB diskům používaným v přenosných datových úložištích, přechodu od mobilních telefonů ke smartphonům a miniaturizace osobních počítačů k tabletům.

Až do poloviny roku 2000 byla technologie NAND Flash z hlediska podílu na trhu za technologií NOR Flash, ale od té doby ji vytlačila. V současné době se technologie NOR většinou omezuje na aplikace, které zahrnují ukládání počítačových dat určených k přímému spuštění (operace typu "execute in place" nebo XiP). Společnost Intel, ST Micro a Spansion (nyní Cypress Semiconductor) jsou jedněmi z hlavních dodavatelů produktů NOR Flash, zatímco Toshiba a Samsung jsou hlavními dodavateli zařízení NAND Flash.

Zatímco u ostatních polovodičových pamětí byla kadence vývoje nových procesních technologií obvykle delší než 2 roky (tj. pomalejší, než předpokládal Moorův zákon), paměti NAND Flash se vyvíjely podstatně rychleji. Na začátku roku 2000 Hwang Chang-gyu ze společnosti Samsung nastínil agresivní plán pro svou společnost a stanovil, že bitová hustota pamětí NAND Flash se musí každý rok zdvojnásobit. Někteří lidé z komunity vývoje flash pamětí začali tento postulát označovat jako "Hwangův zákon" (Dieter, 2014), což je jasný odkaz na Moorův zákon, slavný model, který předpověděl exponenciální vývoj složitosti elektronických zařízení v posledních desetiletích. Dimitrakis (2015) skutečně uvádí, že v posledních letech byla NAND Flash jedinou polovodičovou paměťovou technologií, která se stále vyvíjela tempem srovnatelným s Moorovým zákonem.

Organizace paměti NAND Flash

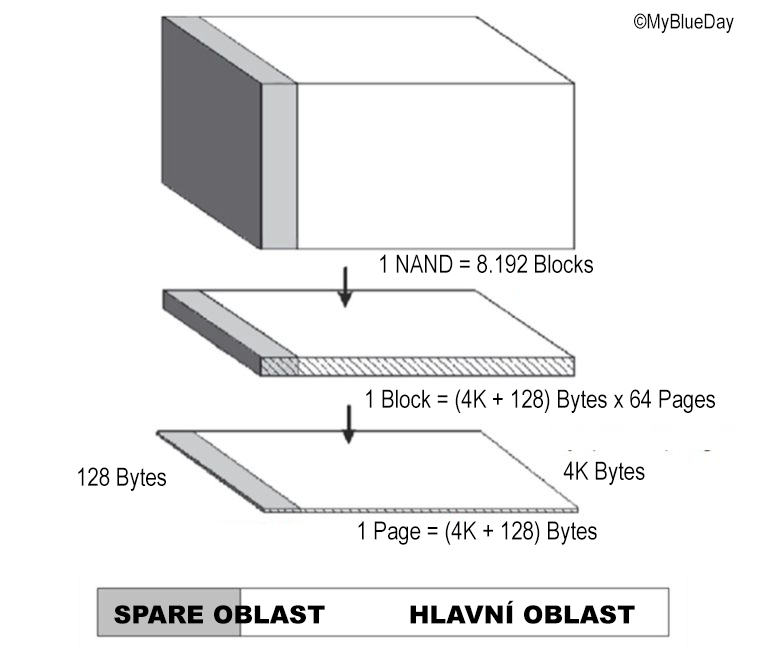

Vnitřní uspořádání paměťového čipu NAND Flash se příliš neliší od jiných paměťových obvodů. Jak je znázorněno na obrázku 2, paměť je rozdělena na stránky a bloky. Blok je nejmenší vymazatelná jednotka. Každý blok obsahuje několik stránek. Počet stránek v bloku je obvykle násobkem 16 (např. 64, 128). Stránka je nejmenší adresovatelná jednotka pro čtení a zápis. Každá stránka se skládá z hlavní oblasti a náhradní oblasti; hlavní oblast může mít velikost od 4 do 8 kilobajtů nebo dokonce 16 kB. Rezervní oblast může být použita pro kódy pro opravu chyb (viz níže) a je řádově několik set bajtů na každé 4 kB hlavní oblasti.

Pokaždé, když má být na zařízení NAND provedena operace, musíme vydat adresu, ve které chceme jednat. Stejně jako u typických pamětí je adresa rozdělena na řádkovou a sloupcovou složku. Řádková adresa identifikuje adresovanou stránku, zatímco sloupcová adresa slouží k identifikaci bajtů uvnitř stránky.

Pole pamětí NOR je adresováno náhodným přístupem, což znamená, že každá buňka může být adresována samostatně, zatímco u pamětí NAND se tak děje sekvenčně. V důsledku toho bývá rychlost mazání u pamětí NAND Flash vyšší než u pamětí NOR Flash. Naproti tomu čtení je u pamětí NOR tech rychlejší než u zařízení NAND. V aplikacích, které čtou data sekvenčně, jako je přehrávání audia/videa nebo záznam dat, je sekvenční provoz výhodou a paměť NAND Flash se stává atraktivní technologií. Pokud jsou však vyžadovány náhodné přístupy, jako v případě provádění kódu, paměti NAND nejsou zdaleka tak výkonné.

Technologie plovoucích hradel

Nejoblíbenější paměťová buňka Flash je založena na technologii plovoucích hradel (FG). V takovém zařízení je tranzistor MOS postaven se dvěma překrývajícími se hradly namísto jednoho; první je zcela obklopeno oxidem, zatímco druhé je kontaktováno a tvoří terminál hradla. Izolované hradlo představuje vynikající "past" pro elektrony, která zaručuje udržení náboje po dlouhá léta. Operace prováděné za účelem injektáže a odstranění elektronů z izolovaného hradla se nazývají programování, resp. mazání. Přiložením pevného napětí na svorky článku je pak možné rozlišit dvě úrovně ukládání: když je napětí na hradle vyšší než prahové napětí Vth článku, je článek zapnutý, v opačném případě je vypnutý. Programování článků NAND je založeno na Fowler-Nordheimově (FN) tunelování, kvantově-mechanickém mechanismu tunelování elektronů v silných elektrických polích. Malá oxidová vrstva mezi kanálem tranzistoru a plovoucím hradlem se vhodně nazývá "tunelový oxid", protože přes ni dochází k transportu elektronů. K FN tunelování studených elektronů dojde, když se přes izolátor vedle plovoucího hradla vytvoří pole o velikosti 8 až 10 MV/cm (zdroj: Brewer a Gill, rok 2008). V závislosti na polaritě elektrického pole mohou být elektrony směrovány do plovoucího hradla nebo z něj ven, což vede k uložení nebo vymazání dat.

Dalším běžným mechanismem přenosu náboje v paměťových buňkách je kanálová injekce horkých elektronů (CHE), kterou lze použít k přidání elektronů do plovoucího hradla (tj. programování). Injekce CHE je rychlejší než tunelování FN, ale je obtížněji ovladatelná a méně účinná. CHE se používá především v zařízeních NOR a v moderních pamětech NAND Flash nenachází uplatnění.

Navzdory zdánlivé jednoduchosti může být manipulace s plovoucími hradly v paměťových buňkách komplikována několika faktory. Zvláště problematická je operace vymazání. Za prvé, vymazávání posouvá prahové napětí negativně z kladné hodnoty na hodnotu blížící se nule; pokud se pokračuje příliš daleko, může prahové napětí projít nulou a stát se záporným. Tento jev, známý jako "overerase", způsobuje přechod tranzistoru z režimu zesílení do režimu vyčerpání. Za druhé, proces vymazávání je citlivý na počáteční stav tranzistoru. Na tranzistory umístěné ve stejné vaničce se současně přivádí mazací napětí. Pokud jsou některé z těchto tranzistorů v naprogramovaném stavu, zatímco jiné jsou ve stavu vymazání, výsledná prahová napětí budou mít značný rozptyl. Je pravděpodobné, že u některých operací dojde k přebuzení. Pro zvládnutí této situace je běžnou praxí naprogramovat všechny tranzistory před přiložením vymazávacího napětí.

Jako u každé digitální paměťové technologie je i u pamětí Flash s plovoucími hradly základním požadavkem spolehlivost. Obecným kritériem je, aby naprogramované prahové napětí Vth nekleslo o 10 % za dobu 10 let, která je pro výrobek relevantní. Počet uložených elektronů s plovoucími hradly v 50 nm zařízení FG NAND pro posun prahového napětí Vth = 4 V je přibližně 600. Kritérium 10% ztráty po dobu 10 let tedy znamená tolerovatelnou ztrátu jednoho elektronu každé dva měsíce nebo únikový proud 3 krát 10-26 A. Převedeno na proudovou hustotu to odpovídá 1 fA/cm2.

V zásadě existuje více cest úniku, které by mohly vést ke ztrátě naprogramovaných nábojů elektronů na plovoucí bráně, ale nejzranitelnější cestou je obvykle únik elektronů přes tunelový oxid, který má být koneckonců jedinou cestou pro transport elektronů v paměťové buňce během programování nebo mazání. Navíc je TOX nejtenčí dielektrickou vrstvou v konfiguraci s plovoucím hradlem. Postupné cykly programování a mazání vedou k tvorbě tzv. oxidových pastí v TOX; jedná se o porušené vazby atomů v oxidové matrici, které vznikají jako vedlejší produkty procesů tunelování elektronů. Hustota pastí se s postupnými cykly programování/vymazávání zvyšuje, což je stav známý jako oxidové napětí.

Existují i další zdroje ztrát elektronů v zařízeních s plovoucími hradly, které se na rozdíl od tunelových úniků oxidů podařilo s rozvojem technologie snížit na přijatelnou úroveň. Například elektrony mohou být zachyceny v izolačních vrstvách obklopujících plovoucí hradlo během zpracování destiček v důsledku tzv. poškození plazmou nebo dokonce během UV expozice, která se obvykle používá k uvedení článku do přesně definovaného stavu na konci procesu "mikrofabrikace". Elektrony se pak mohou časem odchytit, zejména při vysokých teplotách. Změna náboje má za následek změnu potenciálu plovoucího hradla, a tedy snížení prahového napětí článku. Tato zdánlivá ztráta náboje zmizí, pokud se na konci výrobního procesu přidá vhodná tepelná úprava (Bez, 2003).

Počet cyklů mazání je obzvláště důležitý, protože výkonnostní specifikace zařízení, jako je doba mazání bloků nebo doba programování bajtů, jsou zaručeny pouze do maximální specifikace cyklů mazání. Je to proto, že vymazání bloku paměti Flash způsobuje opotřebení oxidové vrstvy izolující plovoucí hradlo, jak bylo uvedeno výše. Specifikace vymazávacího cyklu tak v sobě zahrnuje další důležité ukazatele výdrže; navíc se jedná o velké číslo, často v řádu 105 nebo 106, které ve spotřebitelích vzbuzuje dojem, že jejich data budou bezpečně uložena po dlouhou dobu. Důležité je, že je rozšířeno mylné přesvědčení, že zařízení Flash selže nebo přestane fungovat, jakmile je dosaženo maximální specifikace cyklů. To není pravda; ve většině případů bude zařízení fungovat i po překročení maximální specifikace cyklování. Tento parametr pouze označuje počet vymazání, pro který může výrobce zaručit výkonnostní charakteristiky zařízení.

Kódy pro opravu chyb

Jednou z výhod zařízení NOR Flash je, že většina, ne-li všechny produkty, zaručují 100 % správných bitů při běžných operacích, zatímco zařízení NAND vykazují větší chybovost bitů (BER). Přesto lze čipy NAND vylepšit pomocí kódů pro opravu chyb (ECC), které používají matematické algoritmy k opravě dat, jež se změnila v důsledku degradace buněk paměti Flash nebo jiným způsobem. Stručně řečeno, ECC přidává do zprávy redundantní výrazy, takže při čtení je možné odhalit chyby a obnovit zprávu, která byla s největší pravděpodobností zapsána. Nejoblíbenější ECC, které opravují více než jednu chybu, jsou typu Reed-Solomon nebo BCH.

Algoritmy ECC samozřejmě vyžadují uložení dalších bitů spolu s daty, aby byla zajištěna dostatečná redundance pro opravu chyb. To sice snižuje efektivní kapacitu úložiště, ale oprava chyb může zakrýt nedostatky v zařízení NAND Flash, což umožňuje tolerovat nižší spolehlivost a realizovat pokročilejší návrhy.

MLC a SLC

Konstruktéři vyvinuli řadu řešení, jak snížit náklady na jeden bit pamětí Flash. Nejpředvídatelnějším zlepšením bylo zvýšení počtu bitů přenášených jednou buňkou, což vedlo k vývoji technologie MLC (2 bity/buňka) a později TLC (3 bity/buňka) a QLC (4 bity/buňka). Díky schématu MLC lze velikost čipu snížit na 60 % hodnoty očekávané u jednoúrovňového buněčného schématu SLC (Seiichi, 2016). Tyto návrhy mají samozřejmě své nedostatky; například víceúrovňové buňky vyžadují užší šířky rozdělení prahového napětí, což vede k delší době programování a nižší spolehlivosti, než se očekává u řešení SLC.

Buňky MLC NAND mají také horší odolnost než řešení SLC (zdroj: Micheloni et al., rok 2016). Typické řešení SLC vydrží přibližně 100 000 cyklů programování/vymazání pro každý blok, zatímco řešení MLC je obvykle omezeno na 10 000 cyklů. Z hlediska spolehlivosti je zřejmé, že čím více úrovní je použito, tím více může dojít k poruchám při čtení, což vyžaduje větší schopnost kódu opravovat chyby.

Problém škálovatelnosti u pamětí NAND Flash

V předchozích desetiletích bylo zmenšení velikosti flash buněk dosaženo většinou zmenšením všech rozměrů aktivních (tranzistor flash buněk) i pasivních (propojení) prvků. Technologickým faktorem umožňujícím takový vývoj byl neustálý vývoj pokročilých litografických technik, jako je imerzní litografie, která se zasloužila o dosažení prvků o velikosti 40 až 45 nm.

Škálování v rozsahu 20 nm však brání několik problémů, z nichž nejzřetelnější souvisí s tloušťkou interpolů a tloušťkou tunelových oxidů. Miniaturizace vedla k plovoucím hradlům, která uchovávají stovky nebo dokonce desítky elektronů namísto mnoha tisíc, které se podílely na provozu dřívějších zařízení; v důsledku toho může v malých FG ztráta i několika nosičů náboje vést k vymazání dat (zdroj: Gastaldi a Campardo, rok 2017). Tloušťku tunelových oxidových vrstev, které slouží jako kanály pro tyto nosiče náboje, nelze snadno snížit ze dvou důvodů. Zaprvé, při tloušťce v rozmezí 5 až 6 nm může proud protékat TOX prostřednictvím Fowler-Nordheimova tunelování i bez pomoci elektrického pole, což je nepřijatelné, pokud má paměť fungovat pouze na popud posunu programovacího nebo mazacího napětí. Za druhé, při tloušťce 8 až 9 nm dochází k velkým únikovým proudům s podporou pastí, zejména po opakovaných cyklech zápisu/vymazání. Nakonec si limity při snižování tloušťky oxidu hradla vyžádají použití vysokých napětí při programování a mazání. Závěrečné fáze dekódovacích obvodů nelze zmenšit, protože musí akceptovat tak vysoká napětí, což dále omezuje miniaturizaci pole. Postupný přechod elektronických výrobků na stále nižší provozní napětí (z 5 V na 3,3 V, pak na 1,1 V a nakonec na 0,5 V nebo méně) toto dilema škálovatelnosti jen zhoršuje.

Mezi další problémy při škálování pamětí NAND Flash patří náhodný telegrafní šum (RTN), náhodná fluktuace dopantu (RDF) a problém vzduchové mezery.

S tím, jak pokročilé technologie MOS vstupují do oblasti pod 20 nm, začaly návrhy pamětí Flash vykazovat závažná omezení. Dimitrakis v roce 2015 uvádí, že škálování čipů Flash ze 72 na 20 nm ukázalo zvýšení bitové chybovosti z 10-7 na 10-2 a snížení specifikací cyklování z 10 000 cyklů na méně než 3 000 cyklů. Škálování NAND skutečně zvyšuje hustotu a snižuje náklady rychlým tempem, ale spolehlivost se rychle zhoršuje, což vedlo některé členy komunity Flash k pochybnostem, zda některé produkty Flash, zejména SSD na bázi NAND, budou v blízké budoucnosti nadále nabízet trvale konkurenceschopný poměr cena/výkon.

Současný stav: paměti 3D NAND a paměti se zachycením náboje

Nejslibnějším í způsobem, jak obejít četná omezení sub-20 nm konstrukcí NAND, je výměna planární konstrukce buněk za trojrozměrnou architekturu. Tyto technologie, často sdružované pod souhrnným označením 3D NAND, vycházejí z předpokladu, že použití vertikálního, na sebe kladeného vzoru paměťových vrstev by odstranilo potřebu neustálého škálování technologie.

Architektura 3D NAND může být "vertikální" nebo "horizontální". Ve vertikálním 3D je kanál buněk NAND tvořen tečkami, které kříží vrstvy hradel, a délka kanálu každého tranzistoru řetězce NAND je určena tloušťkou polyvrstvy, zatímco šířka kanálu je určena obvodem tečky. Aby se minimalizovala zabraná plocha, je průměr tečky definován velikostí procesní funkce. Vrstvy hradel jsou společné pro všechny buňky bitové řady a nejsou litograficky definovány. Naproti tomu v horizontálním přístupu se hradla zvedají vertikálně a jsou definována tak, aby se vytvořila délka hradla, zatímco kanály probíhají horizontálně. V tomto případě je šířka kanálu definována tloušťkou kanálové vrstvy. První komerční paměť NAND na bázi 3D, kterou společnost Samsung uvedla na trh v roce 2014, je založena na vertikální 3D architektuře.

Jak uvádí Micheloni v roce 2016, příslibem 3D NAND je, že přechodné náklady, jako jsou náklady na integraci nové technologie s rozhraními SSD, jsou "jednorázové" náklady, které po realizaci umožní čipům 3D NAND dosáhnout nižších hodnot nákladů na bit, než jaké poskytují současné planární produkty NAND. Micheloni (2016) předpokládá, že počáteční růst se bude pravděpodobně soustředit na podniková řešení SSD, protože segment klientských SSD v druhé polovině roku 2010 poněkud ochladl. Lue (v Dimitrakis roku 2015) poznamenává, že pokud by se podařilo úspěšně implementovat 3D architekturu, mohlo by dojít k "resetování" škálování pamětí NAND Flash, což znamená, že konstruktéři by mohli dosahovat stále větší bitové hustoty a zároveň využívat velikosti prvků, které byly před lety standardem u planárních pamětí NAND, jen tentokrát nově poskládaných a uspořádaných trojrozměrně. Díky tomu by alespoň jedna úspěšná architektura 3D NAND mohla zajistit škálovatelnost v blízké budoucnosti.

Časová prodleva mezi první publikací o BiCS (raná architektura 3D NAND, popsaná japonskými výzkumníky v roce 2007) a komerčním uvedením produktu 3D NAND společností Samsung (v roce 2014) činila 7 let, což je na poměry paměťového průmyslu působivě malá doba uvedení na trh; tak krátká prodleva odráží naléhavost komunity Flash při hledání způsobů, jak překonat omezení stávajících technologií NAND, když se škálování dostane na 20nm uzel.

Kromě toho, že inženýři usilují o jinou architekturu, zašli ještě o krok dále a opustili samotnou koncepci plovoucích hradel, která je stará již několik desetiletí. Místo ní začali konstruktéři používat paměti s nábojovou pastí (CT), což je technologie, která byla navzdory své zdánlivé novosti původně navržena v 60. letech 20. století. V CT buňce jsou nosiče vstřikovány a vyvrhovány skrze tunelový oxid podobně jako v plovoucím hradle. Na rozdíl od buněk s plovoucím hradlem, které mají jako paměťový prvek polykrystalickou křemíkovou vrstvu, jsou však v paměti s nábojovou pastí elektrony zachyceny uvnitř vrstvy nitridu křemíku. Paměťová buňka s nábojovou pastí se získá interkalací vrstvy Si3N4 mezi dvě izolační vrstvy SiO2 s vodivou vrstvou poly-Si jako řídicím hradlem. Mnoho elektronových pastí obsažených v nitridové vrstvě tak hraje rovnocennou roli jako plovoucí hradlo.

Tunelový oxid má obvykle tloušťku 2 až 5 nm a umožňuje elektronům přicházejícím z kanálu pohybovat se tunelováním do silnější izolační vrstvy SiN a obsazovat pasti nacházející se uvnitř zakázaného pásu SiN. Elektrony se přenášejí přivedením kladného napětí na řídicí hradlo.

Jednou z důležitých výhod paměťových článků s nábojovými pastmi je, že řídicí hradlo přímo interaguje s elektrony cirkulujícími v kanálu. Stínicí efekt plovoucího hradla se již neprojevuje, a proto odpadá problém vazby mezi řídicím a plovoucím hradlem, který je limitujícím faktorem při problémech týkajících se miniaturizace v FG článcích.

Nahrazení vodivého plovoucího hradla na bázi poly-Si vrstvou Si3N4, která je izolační a bohatá na elektronové pasti, představuje také výhodu ukládání elektronů v odlišných oblastech izolantu. V důsledku toho je dosažení vícebitových článků v provedení s nábojovými pastmi potenciálně snazší než u technologie s plovoucím hradlem (zdroj Lacaze a Lacroix rok 2014).

Závěr

Místo velkých investic spojených s implementací nejmodernější paměti NAND by se inženýři mohli jednoduše zbavit paměti Flash a přijít se zcela novou technologií ukládání dat. Nové technologie nevolatilních pamětí, jako jsou feroelektrické paměti RAM (FeRAM), dosáhly přiměřeného úspěchu a diskuse o nich zaplňují celé svazky (např. Park, 2016). Přesto je jednou z výhod pamětí NAND skutečnost, že zatímco nové paměti vyžadují zcela nový proces integrace se stávajícími digitálními technologiemi, produkty 3D NAND, ať už jsou založeny na buňkách s plovoucími hradly nebo na buňkách s nábojovou pastí, se opírají o více než tři desetiletí zkušeností z výzkumu pamětí Flash a lze je snadno integrovat do současných zařízení. Trojrozměrné konstrukce pamětí NAND dosáhly přiměřeného stupně úspěchu a v kombinaci s moderní technologií nábojových pastí mohou v blízké budoucnosti uspokojit požadavky trhu s paměťmi na bitovou hustotu a přijatelnou cenu.

Odkazy na publikace a použité zdroje

Pro větší pohodlí jsem odborně editované publikace uvedl se jménem editora, protože jsem často použil více než jednu kapitolu a různé kapitoly měly různé autory.

- Bez, R., Camerlenghi, E., Modelli, A. and Visconti, A. (2003). Introduction to Flash memory. Proceedings of the IEEE, 91:4, 489 – 502.

- BREWER, J.E. and GILL, M. (Eds.) (2008). Nonvolatile Memory Technologies with Emphasis on Flash. Hoboken: John Wiley and Sons.

- DIMITRAKIS, P. (Ed.) (2015). Charge-Trapping Non-Volatile Memories: Volume 1. Berlin/Heidelberg: Springer.

- GASTALDI, R. and CAMPARDO, G. (Eds.) (2017). In Search of the Next Memory. Berlin/Heidelberg: Springer.

- LACAZE, P.C. and LACROIX, J.-C. (2014). Non-Volatile Memories. Hoboken: John Wiley and Sons.

- MICHELONI, R. (Ed.) (2016). 3D Flash Memories. Berlin/Heidelberg: Springer.

- MICHELONI, R., MARELLI, A. and ESHGHI, K. (Eds.) (2018). Inside Solid State Drives (SSDs). 2nd edition. Berlin/Heidelberg: Springer.

- PARK, B.-E. et al. (Eds.) (2016). Ferroelectric-Gate Field Effect Transistor Memories. Berlin/Heidelberg: Springer.

- RICHTER, D. (2014). Flash Memories. Berlin/Heidelberg: Springer.

- SEIICHI, A. (2016). NAND Flash Memory Technologies. Hoboken: John Wiley and Sons.